#### **RESEARCH ARTICLE**

OPEN ACCESS

Manuscript received May 2, 2024; revised May 23, 2024; accepted May 27, 2024; date of publication July 28, 2024 Digital Object Identifier (**DOI**): <u>https://doi.org/10.35882/jeeemi.v6i3.400</u>

**Copyright** © 2024 by the authors. This work is an open-access article and licensed under a Creative Commons Attribution-ShareAlike 4.0 International License (<u>CC BY-SA 4.0</u>).

How to cite: L. Sowmiya, S.M. Ramesh, Finney Daniel Shadrach, and A. Arul, "Hybrid Radix-4 SESA/SEDA Adders for Medical Image Processing", Journal of Electronics, Electromedical Engineering, and Medical Informatics, vol. 6, no. 3, pp. 323-331, July 2024.

## Hybrid Radix-4 SESA/SEDA Adders for Medical Image Processing

### L. Sowmiya<sup>®</sup>, S.M. Ramesh<sup>®</sup>, Finney Daniel Shadrach<sup>®</sup>, and A. Arul<sup>®</sup>

Department of Electronics and Communication Engineering, KPR Institute of Engineering and Technology, Coimbatore, India

Corresponding author: Finney Daniel Shadrach (e-mail: finneydaniels@gmail.com).

**ABSTRACT** An adder is characterized as a digital circuit designed to compute the sum of numerical inputs, processing incoming binary digits and outputting their aggregate as a binary number. Digital adders play a crucial role in error-tolerant applications such as machine learning and image processing. However, a significant amount of power is typically consumed by traditional adders, posing challenges for energy-efficient circuit designs. This research is aimed at the development of adders that minimize power consumption without compromising performance, particularly for VLSI chips utilized in error-tolerant applications. A novel integration of hybrid radix-4 adders with Single Exact and Single Approximation (SESA) and Single Exact and Dual Approximation (SEDA) techniques is proposed that is both power-efficient and effective. Comprehensive simulations were conducted using the Xilinx ISE software, demonstrating that our SESA-RDx adders outperform conventional adders by achieving a power usage reduction of up to 58% and enhancing performance speed by up to 26.4%. The proposed hybrid adders signify a significant advancement in low-power adder design, providing a scalable and cost-effective solution for modern digital systems requiring energy efficiency without sacrificing accuracy.

**INDEX TERMS** Approximate Adders, Hybrid radix-4, Image Processing, Power Efficient, Xilinx ISE.

### I. INTRODUCTION

In today's world of electronic systems approximation computing plays a crucial role. It is a computing approach that focuses on findings for accurate solutions to problems instead of exact ones. This method has gained popularity across industries due to the increasing need for energy high performance computing solutions [1]. While approximation computing offers advantages in terms of saving resources and boosting efficiency it is important to consider the balance between accuracy and resource conservation. The decision to embrace approximation computing depends on the requirements of application and the acceptable margin of error in the results. Approximate circuits, also known as inexact or unreliable circuits and they are designed to provide results that fall within a range of error rather than being exact. These circuits find applications in fields where strict precision is not energy efficiency and cost savings are valued [2]. They are particularly useful in image and signal processors for tasks like image resizing, filtering, audio and speech processing well as audio compression where a slight compromise, in quality can be tolerated. These approximate circuits are widely used for hardware accelerators in machine learning and deep learning.

Graphic Processing Units (GPUs) find utility across domains including gaming and scientific simulations. Approximate circuits can be used in graphics rendering to enhance real time performance while maintaining quality within a range. The extent to which approximate circuits are utilized depends on the demands of the application and the permissible margin of error. In some cases, the trade-off between reduced energy consumption, increased speed, and acceptable error margins makes approximate circuits a compelling choice.

Adders are fundamental building blocks in digital electronics and computer systems and it is primarily used for performing arithmetic operations, especially addition [23]. Adders can be found in various applications throughout the field of computing and electronics. Adders are two types and they are accurate and approximation adders. Accurate adders may consume more power and energy compared to approximation adders, making them less suitable for energyefficient circuits. Accurate adders are essential when precision is critical, while approximation adders offer advantages in terms of speed, resource efficiency and energy savings [1]. Approximation adders are a type of digital adder circuit designed to perform addition operations with some degree of approximation. The primary concern of approximation adders is minimizing power consumption, reducing hardware complexity and improving speed. Approximation adders are particularly useful in applications where a small loss in precision is acceptable or even imperceptible, such as multimedia processing, real-time signal processing, or low-power devices like IoT sensors. However, their use should be carefully considered based on the specific requirements of the application [2].

In digital circuits and representations, 'radix' refers to the base of a number system, which plays a crucial role in fields such as digital signal processing and data encoding. In the proposed system, hybrid radix 4 adders are integrated with SESA and SEDA adders for obtaining better simulation results. A hybrid radix-4 adder is a type of digital adder circuit that combines the principles of both radix-4 and nonradix-4 adders to optimize addition operations. Radix-4, radix-8 or other bases that are depends upon the specific application requirements. The goal is to achieve a balance between speed and hardware complexity by exploiting the advantages of different radix approaches.

Mostly in single approximation adders, the Least Significant Bit (LSB) is taken for approximate and Most Significant Bit (MSB) is considered as accurate. But in this proposed scheme, LSB is considered for SESA and SEDA approximation. On the other hand, MSB is maintained with hybrid radix 4 circuit. Radix 4 adder uses parallel computation approach [14]. This may lead to low power energy consumption and reduced delay when compared to other approximate adder circuits. The real time applications are implemented through MATLAB software.

In background work, the previous schemes and works related to hybrid approximation adders are analysed and discussed. Most of the previous works consists of different types of adders and they are described in this section.

Seved et al., in [3] implements a memristor based approximate full adders. This scheme mainly works on the logic of imply methods. The energy consumption is about 68%. Though this system has numerous applications like image addition, image filtering. It lags in providing minimum error rate and commercial availability of memristor is low when compared to other transistors. To overcome this, Ayoub et al., in [4] describes about approximation adders and it follows approach that based upon nanotechnology. The delay of this scheme is given as delay of 2.16 ns and it provides average amount of power consumption when compared to other schemes. This approach gives binary image application. Chandan et al., in [5] describes a combination of imply logic and magic nor approximate adders. In this scheme, kodak datasets are used. Testbench results are simulated with pareto optimal designs and compared with other schemes. This scheme gives better bench mark results but does not mention power consumption and delay clearly. The results of digital image processing are not mentioned in detailed structures.

Gulafshan et al., in [6] presented MTJ hybrid approximate adders. The main target of this scheme is to reduce sensing energy and reduce area size. The proposed work is simulated with the help of HSPICE but does not clearly mention about image processing applications. MTJ uses mechanism known as spintronics and contain ferromagnetic properties. MTJ has numerous applications but this type of adder is costlier when compared to other approximate adders. Jungwon et al., in [7] implements a ERCPAA adder with the mechanism of prediction and truncation methods. Lena image is taken and demonstrated for image processing applications. In comparison with other approximation adders, ERCPAA has average power consumption delay. Other than digital image processing applications, this scheme is used for Neuromorphic computing and machine learning applications.

In order to rectify these approximate full adders disadvantages, Tanfer et al., in [8] proposed a LCA adder with LSB is approximated and MSB kept exactly. Monte carlo simulations were extracted in this scheme. This scheme has better RTL schematic design but lags in providing details about approximation adders real time application and analysis. Waqar et al., in [9] demonstrated LEADx adder for reducing error and it can implement in video processing applications. It has moderate PSNR value for various video sequences.

In [10] Kun et al., shows a hybrid radix 4 circuit for different VLSI applications. ACRA is a radix 4 adder and it works under both approximate and accurate modes. Though it has excellent image processing applications, it lags in providing important parameter low power consumption. Abdolah et al., in [11] describes a spintronic based adder for gaussian filter image processing applications and gives 47% improvements in power consumption. It reduces leakage current but cost of MTJ is not affordable and complex in market availability.

Padmanaban et al., in [12] shows a HOAANED approximate adder in Xilinx Artix-7. These HOAANED adder is experimented by various image dataset but power consumption, delay and other parameters are average when compared to few schemes. Weiqiang et al., in [13] designed an approximation adder for image processing applications. In this scheme they have approached majority logic technique, the circuit demonstrated here is said to be MLAFA and its NMED value is 0.083 [15]. The image processing applications is better when compared to other schemes but it does not provide power consumption and delay parameters [16].

From the existing schemes, overall interpretation of approximation adders is given in this section. Many schemes provide good image processing applications but lags in providing solutions for low power consumption and delay [17]. In most of the scheme's half of the bits are approximated and another half is left without any incorporation of mechanisms or techniques. Huge scheme approaches serial-based processing mechanisms [18]. To overcome these issues, our proposed system uses approximation technique along with fusion of radix 4 adder in MSB. Radix 4 adder works under the principle of parallel computing and reduces propagation delay and increase adder speed [19]. Proposed system uses single approximation techniques, it can work under both accurate and approximation modes.

The main objective of the proposed scheme is to design an efficient approximation adder with a focus on maintaining low energy consumption. Additionally, the aim is to achieve better energy savings and minimize delay in operation. The organization of the remaining parts of our research article is as follows: Section II presents the proposed methodology, Section III elucidates the results obtained, Section IV delves into a comprehensive discussion, and the concluding section is our conclusion.

### II. PROPOSED METHODOLOGY

### A. HYBRID RADIX-4 MECHANISM

Radix-4 works under the principle of parallel computing i.e., proceeding two bits at same time. Due to this, hybrid radix 4 reduces propagation delay, improve power consumption of the system and increase processing speed [20]. Radix-4 consists of five inputs namely  $C_i$ , A,  $A_0$ , B,  $B_0$  and three output is denoted as  $C_o$ ,  $S_i$ ,  $S_{i+1}$ . Here the input  $C_i$  is said to be carry input and A,  $A_0$  denotes augend respectively. The parameter B,  $B_0$  denotes addend respectively [21].  $C_o$ ,  $S_i$ ,  $S_{i+1}$  is said to be carry output and sum of hybrid radix 4 respectively. The Boolean equation for hybrid radix 4 is formularized. Correctness proof (1), (2) and (3)

$$C_o = A_0 B_0 + (AB)(A_0 + B_0) + C_i ((AB)(A_0 + B_0))$$

(1)

$$S_i = (A \oplus B) \oplus C_i \tag{2}$$

$$S_{i+1} = (A_0 \oplus B_0) \oplus (AB + C_i A + C_i B)$$

(3)

The equation (1), (2), (3) denotes the outputs of radix-4 [14]. The Fast Fourier Transform (FFT) algorithm was developed to overcome the computational complexity. In FFT techniques, butterfly structures are used for computation and transforms [22].

### **B. SINGLE APPROXIMATION TECHNIQUES**

Single approximation includes SESA and SEDA adders. Single approximation mechanism operates in accurate and approximate mode [23]. In SESA, single n bit accurate or Exact Part (MSB) approximate addition takes place but in SEDA the approach is quite different. SEDA can perform both single and dual n bit operations for accurate or approximate addition [24].

In SESA, the sum output is approximated and the carry left without approximation. Under single approximation SEDA, sum output is approximated and carry output will be depend upon the previous sum output and generate according to it [25]. Multiplexer is included in SEDA for conversion of sum into carry output. The single approximation technique has maximum bound error [26]. The Boolean function of single approximation adders is given in the equations, correctness proof (4) and (5):

$$C_o = AB + BC + CA \tag{4}$$

$$S = C_o^{`} \tag{5}$$

In equation (4) and (5), A, B and C are input of single approximation [14]. S denotes the sum and  $C_o$  denotes carry output.

# C. INTEGRATION OF HYBRID RADIX-4 WITH APPROXIMATION TECHNIQUE (SESA-RDx and SEDA-RDx)

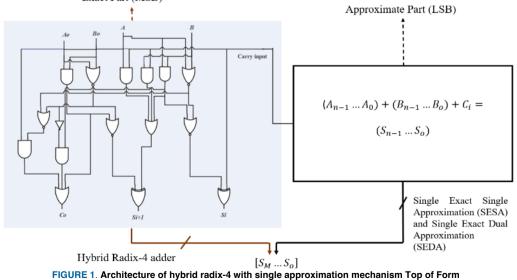

The given Fig. 1 shows the architecture of proposed system. The architecture consists of LSB, MSB parts and the single approximation takes place at LSB [27]. Additionally, at the MSB, exact hybrid radix-4 is exhibited. By using this mechanism propagation delay gets reduced and parameters for a signal processor will be satisfied as per the applications. n denotes the number of bits involved in single approximation mechanism [28]. Moreover, in single approximation mechanism PG signal is induced in input to determine whether the circuit works under accurate or approximate conditions [29].

When PG =1, bits in the sum and carry gets approximated and the circuit undergo approximate mode. Furthermore, when PG =0, under disable conditions circuit will operate in accurate state without any approximation. In inaccurate part, when PG gets enabled, sum gets approximated with

the complement of carry [30]. Under exact part, approximate carry is given as input along with other inputs. In addition to

that accurate i.e., exact part of the adder consists of hybrid radix-4 along with most significant bits are parallelly XOR- ed and OR-ed at last for generating exact sum and carry. Single approximation mechanism exhibits under 8-bit,16-bit states [17]. For example, in 8- bit approximation takes place by approximating 0-3 bits in LSB and bit 4-7 bits in MSB are incorporated by hybrid radix-4 circuit. The output of the single approximation gets fetched and given as input to images in MATLAB software for developing real time applications [22]. Medical images are taken for analysing and diagnosis of several diseases such as brain tumour, neural disease and bone fractures etc., The focus of the proposed system is to give better results for enhanced medical images. The results of medical images are demonstrated and discussed in further sections.

### **III. RESULTS**

Image smoothing is a method used to minimize the unwanted noise in an image by averaging the pixel values in the surrounding area of each pixel. On the other hand, image sharpening is a technique employed to improve the sharpness and intricacies of an image, giving it a more defined and clear appearance by increasing the high-frequency elements of the image. The size of the input image is taken as 256x256 and converted in to grayscale image for generating real time image processing applications. In this part, applications of proposed single approximation namely, image smoothening and image sharpening are simulated in MATLAB and its performance metrics are analyzed.

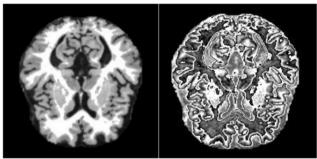

FIGURE 2. Image of Alzheimer Brain

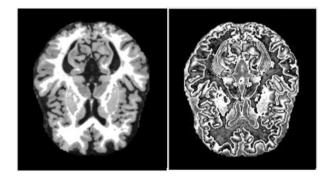

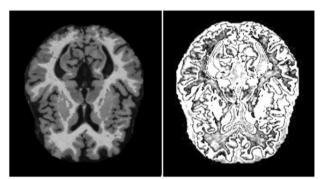

FIGURE 3. Image Smoothening and Sharpening of Existing SESA Adder

FIGURE 4.Image Smoothening and Sharpening Done By Existing SEDA Adder.

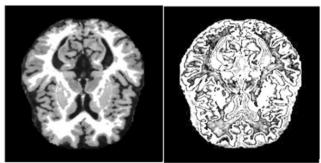

FIGURE 5.Image Smoothening and Sharpening by Proposed SESA-RDx Adder

FIGURE 6.Image Smoothening and Sharpening by Proposed model of SEDA-RDx Adder.

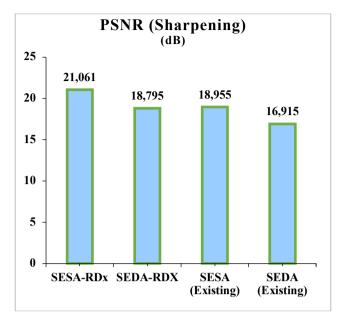

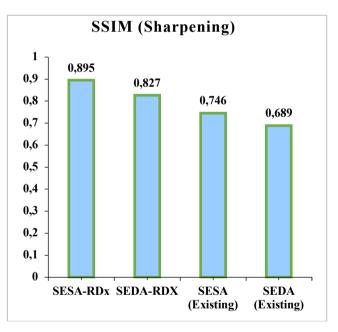

Fig. 2 represents the brain activity image of patient affected by alzheimer disease. 16 bit of SESA- RDx and SEDA- RDx adders are given as input pixels for matlab image simulation. Furthermore, image soothening and sharpening are done for analysing the adder performance. Fig. 3 and 4 shows the applications of existing single approximation adders and Fig. 5, 6 represents applications of SESA-RDx, SEDA-RDx. PSNR stands for Peak Signal-to-Noise Ratio and SSIM stands for Structural Similarity Index Measure. Additionally, these metrics are commonly used to evaluate the quality of processed or reconstructed images in comparison to the original image. Moreover, PSNR and SSIM values are derived for the brain images. Table.1 describe PSNR and SSIM data for given image smoothen and sharpen of alzheimer brain images. Moreover, performance metrics and image simulated by SESA-RDx is well efficient when compared to SEDA-RDx.

| TABLE 1           Metrics of single approximation adders           SINGLE APPROXIMATION ADDERS |        |       |        |       |  |  |  |

|------------------------------------------------------------------------------------------------|--------|-------|--------|-------|--|--|--|

|                                                                                                |        |       |        |       |  |  |  |

| Methods                                                                                        | PSNR   | SSIM  | PSNR   | SSIM  |  |  |  |

| SESA-RDx<br>(proposed)                                                                         | 24.321 | 0.921 | 21.061 | 0.895 |  |  |  |

| SEDA-RDx<br>(proposed)                                                                         | 19.358 | 0.902 | 18.795 | 0.827 |  |  |  |

| SESA<br>(Existing)                                                                             | 21.889 | 0.829 | 18.955 | 0.746 |  |  |  |

| SEDA<br>(Existing)                                                                             | 17.025 | 0.829 | 16.915 | 0.689 |  |  |  |

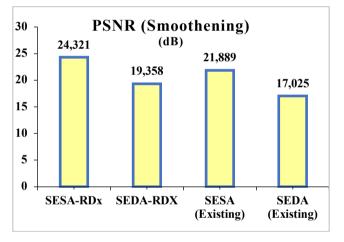

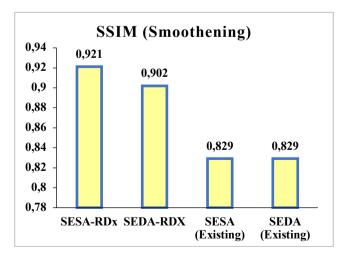

FIGURE 7, FIGURE 8, FIGURE 9, and FIGURE 10 show the graphical representation of PSNR and SSIM of approximation adders applications. From the figure, it is described that highest PSNR and SSIM values are 24.321 and 0.921. Higher PSNR gives clear and accurate images as well as prediction of chronic disease will be easier.

FIGURE 7. Comparison of Smoothening Metrics

FIGURE 8. SSIM Smoothening Parameters of Single Approximation Adders

FIGURE 9. Image Sharpening Parameters

FIGURE 10. SSIM Parameters of Approximation Adders

### **IV.DISCUSSION**

In Xilinx, Look-Up Tables (LUTs) serve as customizable memory blocks capable of executing logic functions, while Flip-Flops act as fundamental storage units holding individual bits of data. Gate delay represents the time required for logic gates to generate output signals upon receiving input signals, crucial for assessing operational speed. Power consumption is a pivotal consideration in system design, impacting energy efficiency and operational costs. Meanwhile, delay signifies the time taken for signals to traverse different components within Xilinx, directly influencing system timing and overall performance.

| TABLE 2           Comparison of approx. adders |     |    |            |              |               |  |  |

|------------------------------------------------|-----|----|------------|--------------|---------------|--|--|

| Adder<br>Design                                | LUT | FF | Gate Delay | Power<br>(W) | Delay<br>(ns) |  |  |

| APPROX 5                                       | 32  | 97 | 0.198      | 0.202        | 3.84          |  |  |

| HEAA                                           | 28  | 88 | 0.190      | 0.201        | 3.19          |  |  |

| HOAANED                                        | 30  | 90 | 0.189      | 0.192        | 2.95          |  |  |

| SESA (Exist)                                   | 27  | 88 | 0.098      | 0.092        | 3.36          |  |  |

| SEDA (Exist)                                   | 27  | 86 | 0.097      | 0.087        | 2.86          |  |  |

| SESA-RDx<br>(Proposed)                         | 25  | 79 | 0.097      | 0.085        | 2.99          |  |  |

| SEDA-RDx<br>(Proposed)                         | 24  | 73 | 0.095      | 0.083        | 2.83          |  |  |

In the realm of approximate adders, single approximation adders demonstrate superior efficiency compared to traditional counterparts due to the elimination of unnecessary transistor components and the utilization of pass transistors. Particularly noteworthy is the incorporation of the hybrid RD4 component at the Most Significant Bit (MSB), facilitating parallel computing and resulting in reduced resource utilization, power consumption, and delay. Moreover, this hybrid approach not only enhances computational efficiency but also fosters clearer input images and more accurate predictions, especially in applications such as chronic disease diagnosis.

The integration of hybrid approaches that combine various approximation techniques or dynamically select the most suitable technique for different function segments holds promise, particularly in medical imaging applications. By leveraging the strengths of different approximation methodologies, these hybrid approaches can enhance the efficiency and accuracy of medical imaging techniques, ultimately contributing to improved diagnostic capabilities and patient outcomes.

TABLE 1 compares different single approximation adders based on their performance in image processing tasks, specifically smoothing and sharpening. The proposed SESA-RDx adder outperforms others in both tasks, according to these metrics. Table 2 represents various adder designs such as APPROX 5, HEAA, HOAANED, SESA (Existing), SEDA (Existing), SESA-RDx (Proposed), and SEDA-RDx (Proposed), comparing and discussing their characteristics. TABLE 2 highlights the trade-offs between power consumption and delay across different adder designs. The proposed SEDA-RDx design stands out as the most efficient

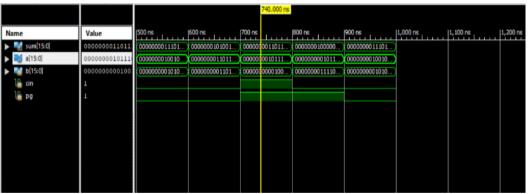

FIGURE 11. Simulation of proposed SESA-RDx

|               |              |   |               |               |               |               | 800.000 ns    |               |                 |

|---------------|--------------|---|---------------|---------------|---------------|---------------|---------------|---------------|-----------------|

| Name          | Value        |   | 400 ns        | 500 ns        | 600 ns        | 700 ns        | 800 ns        | 900 ns        | 1,000 ns  1,100 |

| 🕨 📲 sum(15:0) | 000000100000 | 0 | 0000000100000 | 0000000011101 | 0000000101001 | 0000000011011 | 0000000100000 | 0000000011101 |                 |

| þ 📑 a[15:0]   | 000000001011 | 0 | 0000000001011 | 0000000010010 | 0000000011011 | 0000000010111 | 0000000001011 | 0000000010010 |                 |

| ▶ 🖏 b[15:0]   | 000000011110 | 0 | 0000000011110 | 0000000001010 | 000000001101  | 0000000000100 | 0000000011110 | 0000000001010 |                 |

| 🏰 cin         | 0            |   |               |               |               |               |               |               |                 |

| ዀ pg          | 1            |   |               |               |               |               |               |               |                 |

|               |              |   |               |               |               |               |               |               |                 |

|               |              |   |               |               |               |               |               |               |                 |

|               |              |   |               |               |               |               |               |               |                 |

|               |              |   |               |               |               |               |               |               |                 |

|               |              |   |               |               |               |               |               |               |                 |

|               |              |   |               |               |               |               |               |               |                 |

FIGURE 12. Proposed SEDA- RDx simulated results

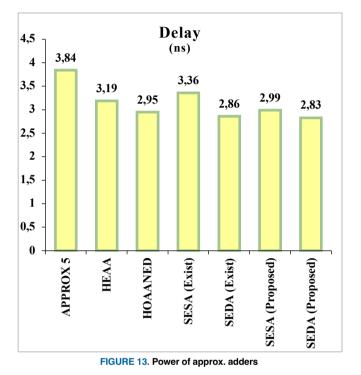

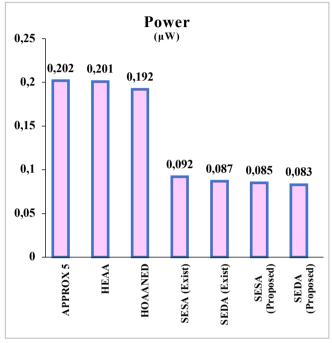

in terms of power while also offering competitive delay times, making it potentially valuable for applications where power efficiency is crucial. FIGURES 11 and FIGURE 12 depict the 16-bit SESA-RDx and SEDA-RDx simulations, while FIGURES 13 and FIGURE 14 provide graphical representations of power and delay for various approximate adders. It is observed in the figures that the power and delay of APPROX 5 are much greater than other approximate adders, while the proposed SEDA-RDx shows significantly lower values compared to various other adders.

TABLE 2 provides an in-depth analysis of various approximate adder designs, aiming to offer a comprehensive understanding of their performance characteristics and tradeoffs. Our investigation encompasses a range of crucial metrics, including the utilization of Look-Up Tables (LUTs) and Flip-Flops (FFs), gate delay, power consumption, and overall delay. These metrics are pivotal in assessing the suitability of adder designs for different application scenarios.

Among the adder designs evaluated, the HOAANED design stood out with its remarkable achievement of the lowest gate delay, clocking in at just 2.95 nanoseconds. This swift processing capability makes it particularly well-suited for applications where rapid response times are imperative. On the other hand, the SEDA-RDx (Proposed) design showcased exceptional power efficiency, consuming a mere 0.083 Watts. Such low power consumption is crucial for energy-conscious applications, offering potential benefits in terms of reduced operational costs and extended battery life in portable devices.

Furthermore, our analysis revealed that the existing SEDA design exhibited the lowest overall delay, completing computations in just 2.86 nanoseconds. This finding

underscores its efficacy in scenarios requiring high-speed processing, such as real-time signal processing or data streaming applications. However, it's important to note that each design presents its own set of advantages and limitations, necessitating careful consideration of the specific requirements and constraints of the target application.

FIGURE 14. Delay of approx. adders

Xilinx simulation is conducted using tools such as the Design Suite to ensure the functionality and timing of hardware designs on Xilinx programmable logic devices. In the simulation, when the input signal is 1, the approximation of the adder takes place at 400 ns by approximating the first and last bit of the adder. This approach, while ensuring efficient approximation, inadvertently introduces а unique characteristic: when the adder operates in its accurate range, it triggers an error rate that subtly extends the processing time. This feature, initially appearing as a limitation, actually enhances the robustness of the scheme by dynamically adjusting the approximation precision based on the input signal, thereby contributing to a more adaptable and reliable system performance. Our study sheds light on the intricate interplay between performance metrics and design choices in the realm of approximate adder implementations. By providing insights into the relative strengths and weaknesses of different designs, we aim to empower designers to make informed decisions when selecting the most suitable adder architecture for their applications. Moving forward, further research endeavors could explore avenues for optimizing these designs to strike a more balanced compromise between speed, power efficiency, and resource utilization, thereby catering to a broader spectrum of application needs. Overall, our study contributes valuable insights to the ongoing

discourse on approximate adder design, facilitating advancements in FPGA-based system implementations.

### V. CONCLUSION

This study successfully demonstrated the capabilities of single-approximation adders for improving medical image quality through smoothing and sharpening techniques. The evaluation of these adders reveals their potential for broad implementation across various technological domains, including microprocessor design. A critical analysis indicates that the APPROX 5 adder consumes 0.202 W of power, which is marginally higher than that of its counterparts. In contrast, the newly introduced SEDA-RDx demonstrates superior efficiency, with a power consumption of only 0.083 µW and a delay of 2.83 ns, outperforming other approximate adders in the field. The study further establishes that SESA-RDx outperforms SEDA-RDx in application performance metrics. Particularly in medical imaging, the deployment of SESA-RDx promises to significantly enhance image clarity, thereby improving the accuracy of chronic condition diagnoses. This research's ambition extends to the development of a MAC circuit with the aim of delving deeper into its practical applications.

### REFERENCES

- X. Fan, T. Zhang, H. Li, H. Liu, S. Lu and J. Han, "DACA: Dynamic Accuracy-Configurable Adders for Energy-Efficient Multi-Precision Computing," in IEEE Transactions on Nanotechnology, vol. 22, pp. 400-408, 2023. https://doi.org/10.1109/TNANO.2023.3297325.

- [2]. H. Seo and Y. Kim, "A Low Latency Approximate Adder Design Based on Dual Sub-Adders With Error Recovery," in IEEE Transactions on Emerging Topics in Computing, 11(3),811-816, (2023). https://doi.org/10.1109/TETC.2023.3270963.

- [3]. S. E. Fatemieh, M. R. Reshadinezhad and N. Taheri Nejad, "Fast and Compact Serial IMPLY-Based Approximate Full Adders Applied in Image Processing," in IEEE Journal on Emerging and Selected Topics in Circuits and Systems, 13(1), 175-188, 2023. https://doi.org/ 10.1109/JETCAS.2023.3241012.

- [4]. A. Sadeghi, R. Ghasemi, H. Ghasemian and N. Shiri, "High Efficient GDI-CNTFET-Based Approximate Full Adder for Next Generation of Computer Architectures," in IEEE Embedded Systems Letters, 15(1), 33-36, (2023). https://doi.org/10.1109/LES.2022.3192530.

- [5]. C. K. Jha, P. L. Thangkhiew, K. Datta and R. Drechsler, "IMAGIN: Library of IMPLY and MAGIC NOR-Based Approximate Adders for In-Memory Computing," in IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, 8(2), 68-76,(2022). https://doi.org/10.1109/JXCDC.2022.3222015.

- [6]. Gulafshan, M. A. Khan and M. Hasan, "Design of High Speed, Energy, and Area Efficient Spin-Based Hybrid MTJ/CMOS and CMOS Only Approximate Adders," in IEEE Transactions on Magnetics, 58(5), 1-8, (2022). https://doi.org/ 10.1109/TMAG.2022.3155968.

- [7]. J. Lee, H. Seo, H. Seok and Y. Kim, "A Novel Approximate Adder Design Using Error Reduced Carry Prediction and Constant Truncation," in IEEE Access, 9,119939-119953, (2021). https://doi.org/10.1109/ACCESS.2021.3108443.

- [8]. T. Alan and J. Henkel, "Probability-Driven Evaluation of Lower-Part Approximation Adders," in IEEE Transactions on Circuits and Systems II: Express Briefs, 69(1), 204-208, (2022). https://doi.org/10.1109/TCSII.2021.3093984.

- [9]. W. Ahmad, B. Ayrancioglu and I. Hamzaoglu, "Low Error Efficient Approximate Adders for FPGAs," in IEEE Access, 9, 117232-117243, (2021). https://doi.org/10.1109/ACCESS.2021. 3107370.

- [10]. K. L. Tsai, Y. -J. Chang, C. -H. Wang and C. -T. Chiang, "Accuracy-Configurable Radix-4 Adder With a Dynamic Output Modification Scheme," in IEEE Transactions on Circuits and Systems I: Regular

Homepage: jeeemi.org\_

Papers, **68**(8), 3328-3336, (2021).https://doi.org/10.1109/TCSI.2021.3085572.

- [11]. A. Amirany, G. Epperson, A. Patooghy and R. Rajaei, "Accuracy-Adaptive Spintronic Adder for Image Processing Applications," in IEEE Transactions on Magnetics, 57(6), 1-10, (2021). https://doi.org/10.1109/TMAG.2021.3069161.

- [12]. P. Balasubramanian, R. Nayar, D. L. Maskell and N. E. Mastorakis, "An Approximate Adder With a Near-Normal Error Distribution: Design, Error Analysis and Practical Application," in IEEE Access, 9, 4518-4530, (2021). https://doi.org/10.1109/ACCESS.2020.3047651.

- [13]. W. Liu, T. Zhang, E. McLarnon, M. O'Neill, P. Montuschi and F. Lombardi, "Design and Analysis of Majority Logic-Based Approximate Adders and Multipliers," in IEEE Transactions on Emerging Topics in Computing, 9(3), 1609-1624, (2021). https://doi.org/ 10.1109/TETC.2019.2929100.

- [14]. A. Arul, M. Kathirvelu. "Design a novel 1-bit full adder with hybrid logic for full-swing, area-efficiency and high-speed". Analog Integr Circ Sig Process (2023). https://doi.org/10.1007/s10470-023-02217-0.

- [15]. Choudhary, P., Bhargava, L., Singh, V. "Approximate Adder Circuits: A Comparative Analysis and Evaluation". In: Yadav, R.P., Nanda, S.J., Rana, P.S., Lim, MH. (eds) Proceedings of the International Conference on Paradigms of Computing, Communication and Data Sciences. Algorithms for Intelligent Systems. Springer, (2023). https://doi.org/10.1007/978-981-19-8742-7\_42.

- [16]. Rajasekhar Turaka, KoteswaraRao Bonagiri, TallaSrinivasa Rao, GundugontiKishore Kumar, Sudharsan Jayabalan, V.Bharath Sreenivasulu, AsisaKumar Panigrahy & M.Durga Prakash "Design of approximate reverse carry select adder using RCPA", International Journal of Electronics Letters, **11**(2), 146-156 (2023). https://doi.org/10.1080/21681724.2022.2062791.

- [17]. Elahe Baratalipour, Arezoo Kamran, SAMA: Self-adjusting multicycle approximate adder, Microelectronics Journal, Volume 134, 2023, 105740, ISSN 0026-2692, https://doi.org/10.1016/j.mejo.2023.105740.

- [18]. Farshid Ahmadi, Mohammad R. Semati, Hassan Daryanavard, Atefeh Minaeifar, Energy-efficient approximate full adders for errortolerant applications, Computers and Electrical Engineering, Volume 110, 2023, 108877, ISSN 0045-7906, https://doi.org/10.1016/j.compeleceng.2023.108877.

- [19]. Ahmadi F, Semati MR, Daryanavard H. A low-power improvedaccuracy approximate error-report-propagate adder for DSP applications. Circuits Syst Signal Process 2023. https://doi.org/10.1007/s00034-023-02291-9. 2023/01/24.

- [20]. Que, HH., Jin, Y., Wang, T. et al. A Survey of Approximate Computing: From Arithmetic Units Design to High-Level Applications. J. Comput. Sci. Technol. 38, 251–272 (2023). https://doi.org/10.1007/s11390-023-2537-y.

- [21]. Ullah, S., Kumar, A. (2023). Designing Application-Specific Approximate Operators. In: Approximate Arithmetic Circuit Architectures for FPGA-based Systems. Springer, Cham. https://doi.org/10.1007/978-3-031-21294-9\_5.

- [22]. M. Rafiee, N. Shiri, and A. Sadeghi, "High-performance 1-bit full adder with excellent driving capability for multistage structures," IEEE Embedded Syst. Lett., vol. 14, no. 1, pp. 47–50, Mar. 2022. https://doi.org/10.1109/LES.2021.3108474.

- [23]. F. Karimi, R. F. Mirzaee, A. Fakeri-Tabrizi, and A. Roohi, "Ultrafast, high-performance 8×8 approximate multipliers by a new multicolumn 3,3:2 inexact compressor and its derivatives," 2021, arXiv:2107.11881.C. Niemann, M. Rethfeldt, and D. Timmermann, "Approximate multipliers for optimal utilization of FPGA resources," in Proc. 24th Int. Symp. Design Diag. Electron. Circuits Syst. (DDECS), Vienna, Austria, Apr. 2021, pp. 23–28.

- [24]. T. Alan, A. Gerstlauer, and J. Henkel, "Runtime accuracyconfigurable approximate hardware synthesis using logic gating and relaxation," in Proc. IEEE Design Autom. Test Europe Conf. Exhibit. (DATE), 2020, pp. 1578–1581.

- [25]. M. Mirzaei and S. Mohammadi, "Low-power and variation-aware approximate arithmetic units for image processing applications,"

AEU Int. J. Electron. Commun., vol. 138, Aug. 2021, Art. no. 153825.

- [26]. Junqi Huang, Nandha Kumar Thulasiraman, Haider Almurib, et al. Analysis of Approximate adders with single functional error. TechRxiv. January 02, 2024. https://doi.org/10.36227/techrxiv.170420873.33149305/v1.

- [27]. Shah Oveisi, S., Roodaki, H., Rezaalipour, M. et al. A powerefficient approximate approach to improve the computational complexity of coding tools in versatile video coding. *Multimed Tools Appl* (2024). https://doi.org/10.1007/s11042-024-18513-4.

- [28]. Damsgaard H, Ometov A and Nurmi J. (2023). Verification of Approximate Hardware Designs with ChiselVerify 2023 IEEE Nordic Circuits and Systems Conference (NorCAS). 10.1109/NorCAS58970.2023.10305474. 979-8-3503-3757-0. (1-7). https://ieeexplore.ieee.org/document/10305474.

- [29]. Nishanth, R., Sulochana, C.H. A novel lightweight CNN-based errorreduced carry prediction approximate full adder design for multimedia applications. *Neural Comput & Applic* 36, 6421–6440 (2024). https://doi.org/10.1007/s00521-023-09316-z.

- [30]. Malik, A., Hussain, M.S. & Hasan, M. Energy-Efficient Exact and Approximate CNTFET-Based Ternary Full Adders. *Circuits Syst* Signal Process (2024). https://doi.org/10.1007/s00034-023-02589-8.

### BIOGRAPHY

**Sowmiya L** received B.E Electronics and Communication Engineering degree from Sri Ramakrishna Engineering College, affiliated to Anna University, Coimbatore in 2021. Currently she is pursuing M.E VLSI Design at KPR Institute of Engineering and Technology, Coimbatore. Her research interests

include network security and digital electronics.

**S.M.Ramesh** received the B.E degree in Electronics and Communication Engineering from Regional Engineering College (Currently NIT) Trichy -Bharathidhasan University and the M.E, degree in Applied Electronics from R.V.S. College of Engineering and Technology, Dindugal - Anna

University, Chennai. He has completed his Ph.D. degree in Information & Communication Engineering from Bannari Amman Institute of Technology, Sathyamangalam - Anna University, Chennai. He has more than 20 years of teaching experience. At present, he is working as Professor in the Department of Electronics and Communication Engineering, KPR Institute of Engineering & Technology, Coimbatore, Tamil Nadu. His current research focuses on Image Processing, Low Power VLSI Design and Embedded Systems. He has published 106 articles in National and International Journals and more than 44 papers in International and National Conferences. He is a life member of (ISTE) Indian Society of Technical Education and member of (IETE) Institution of Electronics and Telecommunications Engineers.

**Finney Daniel Shadrach** holds a Bachelor's degree in Electronics and Communication Engineering, a Master's

degree in Communication Systems, and a Ph.D. degree. from Anna University. Currently, he is serving as an Assistant Professor at KPR Institute of Engineering and Technology in Coimbatore, India. His research interests includes signal processing,

image processing, optimization techniques, and deep learning. He has published more than 30+ research articles in reputed international conferences and journals. He is an active reviewer for esteemed journals such as Springer, Sage, etc., He is a lifetime member of ISTE and a member of IEEE.

A Arul completed his Bachelor's in Electronics and Communication Engineering from Arunai Engineering College, affiliated with Anna University, Chennai, in 2008. He earned his Master's in Applied Electronics from IFET College of Engineering in 2014, ranking 27th.

Currently pursuing a PhD in Information and Communication Engineering at Anna University, Chennai, his research focuses on low-power VLSI design, energy efficiency, and harvesting.